第12回LSIデザインコンテスト・イン沖縄 設計仕様書 - 9

10.LEVEL1:基本課題

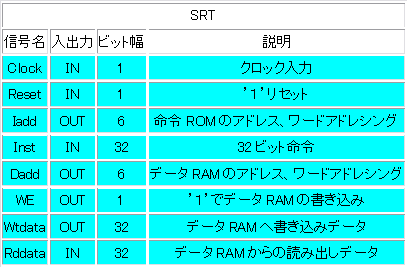

基本課題では図7に示すような、構成での設計である。バブルソートを実行し、動作することを確認せよ。以下にSRTの 入出力ピンを示す。

表9 基本課題用ピンリスト

11.LEVEL2:自由課題

自由課題では、SRTを自由に変更・拡張してください。以下に拡張案を示します。

(1) パイプライン化 : パイプライン動作化にすることで、サイクルタイムを削減し高性能化が可能と思われる。

(2) 命令の追加など自由な拡張

12.スピードと面積の単位

琉球大学以外からの参加の場合、同一のシノプシスデザインコンパイラの論理合成用ライブラリを使用することが困難であるので、

・2入力EXORゲイト1つの遅延時間を 1UNIT_DELAY

・2入力EXORゲイト1つの面積を 1UNIT_AREA

とします。

具体的には、以下のような多段EXOR回路を例に従って合成し最適化し、その1段あたりの遅延時間を 単位時間としてスピードの単位とします。

この例では6段のEXOR段が合成され、クリティカルパス遅延は

report_timingコマンドにより7.17であった

ので、7.17/6=1.195を単位(1UNIT_DELAY)とします。

・例えば、ある遅延が20ならば、20/1.195=17.74UNIT_DELAYとします。

・琉大情報のライブラリ使用者は上記値で換算すればよいです。

また、面積はreport_areaコマンドのtotal cell areaは147.0であり、EXORゲイト数は49個であるので、

147.0/49=3.0を単位(1UNIT_AREA)とします。

・たとえばある回路面積が200ならば、200/3.0=66.67UNIT_AREAとします。

・琉大情報のライブラリ使用者は上記値で換算すればよいです。