| Japanese | English |

設計仕様書

1. ノイズ除去アルゴリズム1-1.スペクトル・サブトラクション法

1-2.可変音声分布を利用したMAP推定法

1-2-1.MAP推定法

1-2-2.T.LotterとP.Varyの音声スペクトル分布

1-2-3.可変音声分布

2. 雑音除去システムの実装

2-1.ハード・ソフトの切り分け

2-1-1.HW・SWの特徴

2-1-2.雑音除去システムにおける処理の特徴

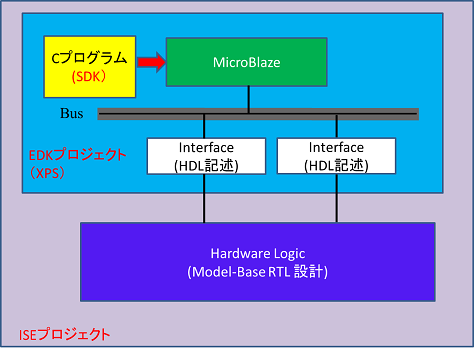

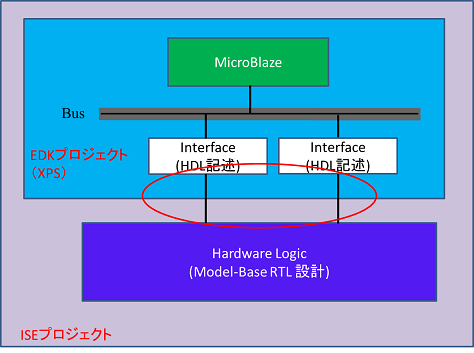

2-1-3.アーキテクチャ

2-2.ハードウェア

2-2-1.処理の流れ

2-2-2.回路構成

2-2-3.HWタイミング

2-3.ソフトウェア

2-3-1.ソースコード

2-3-2.フローチャート

3. 開発環境

3-1.ハードウェア設計手順

3-1-1.Hardware Logicの設計

3-1-2.Xilinx ISE 及び EDKの使い方

3-2.ソフトウェア設計手順

4. 課題

5. スピード及び回路規模の測定単位

6. 参考文献

7. ダウンロード

第17回LSIデザインコンテスト・イン沖縄 設計仕様書 - 3-1

3-1. ハードウェア設計手順

ここから開発手順について説明を行うが,これ以外の手法も多数あるので,これ以外の手法については各自調べてください.

3-1-1. Hardware Logicの設計

今回はSimulinkを用いてハードウェアのRTL設計をモデルベースで行う.設計後,edfファイルにラッピングする.

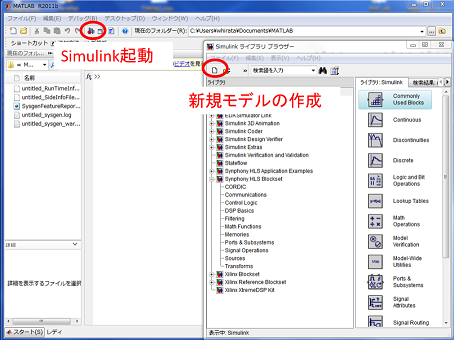

1. MATLABを起動し,Simulinkを立ち上げる.Simulinkライブラリブラウザーが立ち上がったら,画面上部のメ

ニューからファイル→新規作成→新規モデルを選択し,設計画面を開く.

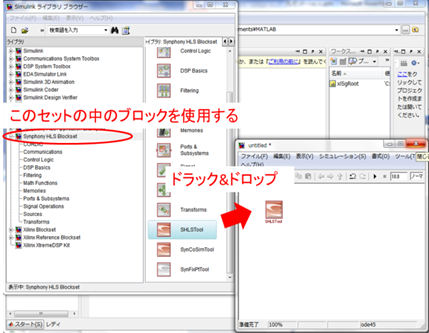

2. ライブラリの中から使用したいブロックを選択し,ドラッグ&ドロップで設計画面に設置することで設計を行え

る.今回はSynplifyを用いて論理合成を行うので,Synphony HLS Blocksetの中からブロックを選び回路設

計を行う.

3. 回路設計後,HDLファイル(.v,.vhd)を生成するためにHLS Blocksetの中からSHLSToolブロックを使用する.

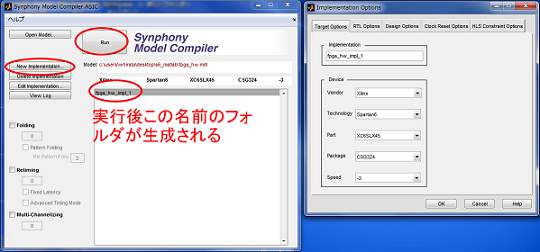

SHLSToolをダブルクリックし,合成画面を開き,New implementationを選択すると,Implementation Options

画面が開く.ここで,使用するデバイスの選択をする.

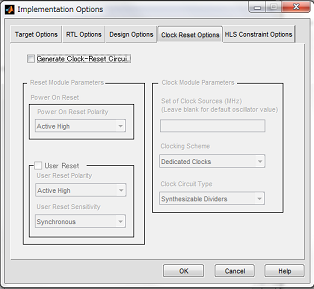

4. Clock Reset OptionsのタブのGenerate Clock-Reset Circuitのチェックを外す.

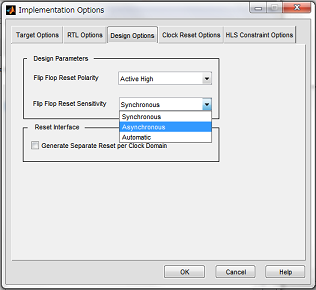

5. Design Optionsタブ内のFlip Flop Reser SensisiviltyをAsyncronusに設定する.

6. 設定後,保存し,Runで実行を行うと,MATLABのフォルダにインプリメントされたファイルを含むフォルダが生

成される.このフォルダの下に\verilogと\vhdlのフォルダがあり,その下にmodel-Base設計した回路が記述さ

れたHDLファイル(.v,.vhd)とプロジェクトファイル(.prj)が生成される.

*作成したモデルファイル(fpga_hw.mdl)はここからダウンロードできる.

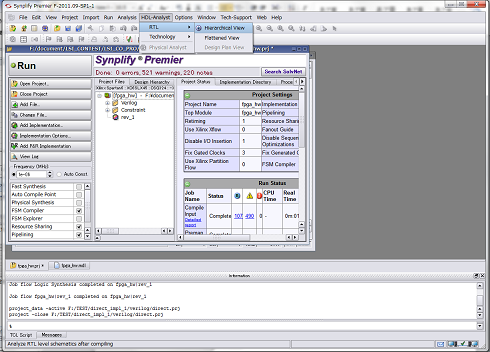

1. Synplify Premierを起動する.画面上部のメニューからFile→Openを選択.SHLSToolで生成されたverilogフォル

ダ内のプロジェクトファイル(fpga_hw_impl_1\verilog\fpga_hw.prj)を開く

2. 画面左にあるImplementation Optionsをクリックする.

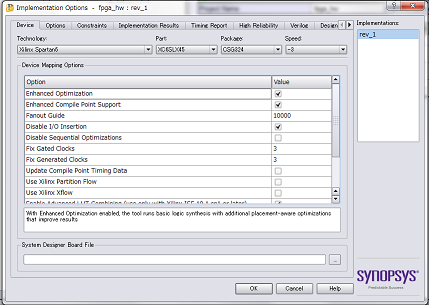

3. Disable I/O Insertionにチェックをいれる.OKをクリック.

4. Runで実行する.fpga_hw_impl_1\verilogにrev_1フォルダが作成され,その中にedfファイルが作成される.

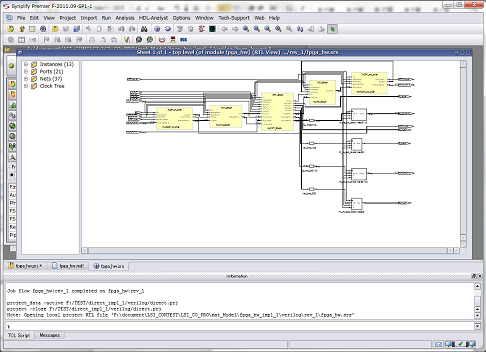

5. 画面上部のメニューのHDL-Analyst→RTL→Hierarchical Viewをクリックする.

6. 生成したedfファイルの回路構成を見ることができる.

*作成したedfファイル(fpga_hw.edf)はここからダウンロードできる.

RTLソースが欲しい方はこちらまで連絡ください。

3-1-2. Xilinx ISE 及び EDKの使い方

今回,ATLYSボードに付属するAC97 AUDIO CODEC を使用するに当たり,AC97をMicroBlazeで制御するデモプロジェクトである Atlys_AC97_EDK_demoを参考に開発を行った.このデモはDIGILENT社のATLYSのHPからダウンロードできる.このデモを動かすためには, ISE13.2以降のバージョンのEDKが必要となる.下記に実行手順をまとめる.

1. HPからダウンロードしてきたAtlys_AC97_EDK_demo.zipを解凍する.

2. EDKのツールであるxps(Xilinx Platform Studio)を起動する.

3. 画面上部のメニューからFile→Open projectを選択し,Atlys_AC97_EDK_demoフォルダ下のprojectフォルダ

内のsystem.xmpを選択する.

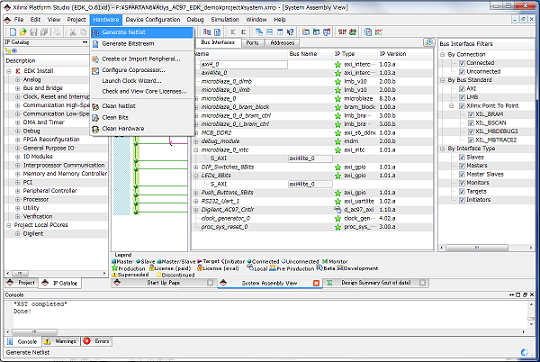

4. 画面上部のメニューの中からHardware→Generate Netlistをクリックする.

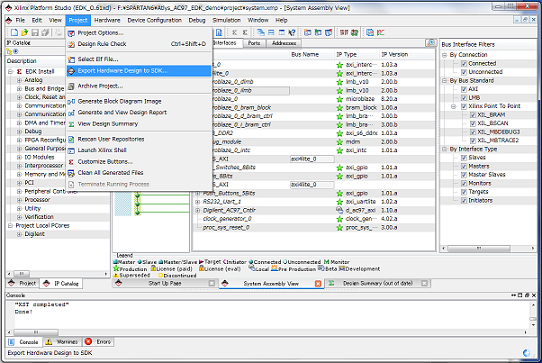

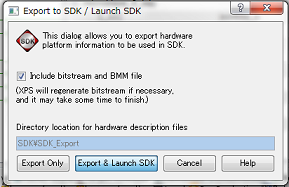

5. インプリメントが終了したら,画面上部のメニューからProject→Export Hardware Design to SDK を選択する.

6. Export & Launch SDKを選択する.

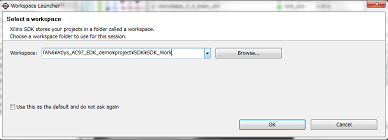

7. Atlys_AC97_EDK_demo\project\SDKのフォルダの下にSDK_Workフォルダを作成して,Workspaceにセットす

る.OKを押す.

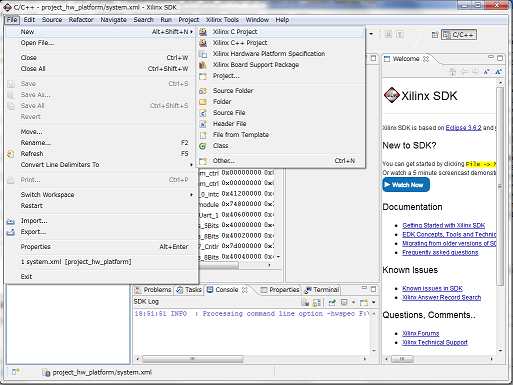

8. SDKが起動する.画面上部のメニューの中からFile→New→Xilinx C Projecetを選択する.

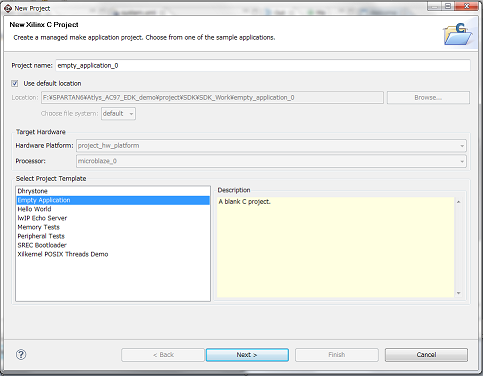

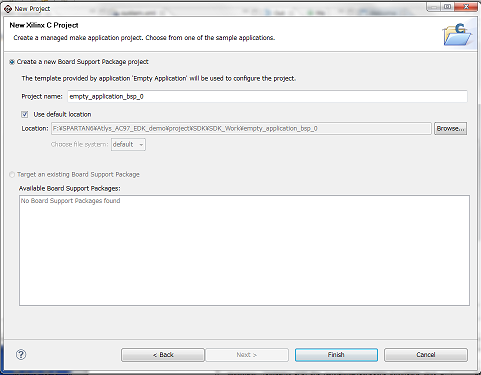

9. New Projectが開く.Select Project Template欄からEmpty Applicationを選択する.Nextを選択する.

10. Create a new Board Support Package project が選択されているのを確認してFinishをクリック.

11. Project Explorer にCプロジェクトとBSPプロジェクトのフォルダが追加される.

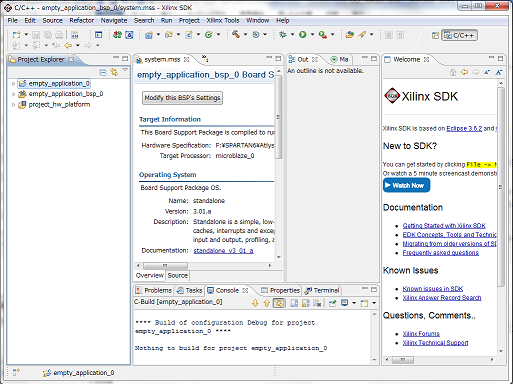

12. Atlys_AC97_EDK_demo\source\内のファイルを全てAtlys_AC97_EDK_demo\project\SDK\SDK_Work

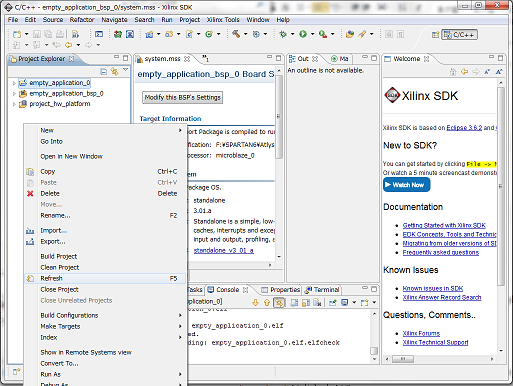

\empty_application_0\srcにコピーする.その後Project Explorer内で右クリック→Refreshを選択すると,

Projectが更新され,Project Explorerにソースが追加される.

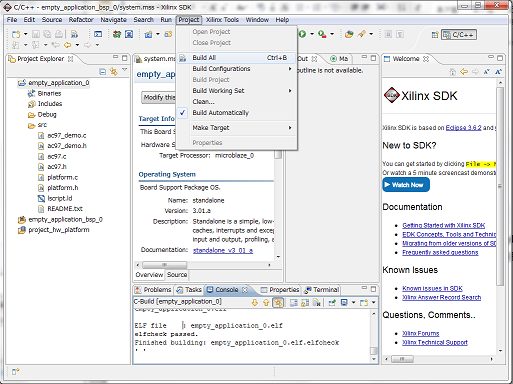

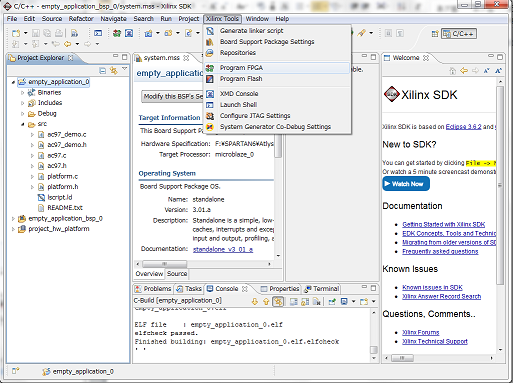

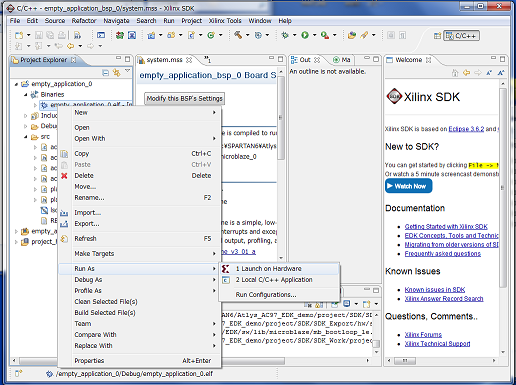

13. 画面上部のメニューのProjectの中からBuild Allを選択する.

14. Atlysの電源を入れPROGポートにコネクタをさす.画面上部のメニューのXilinx Tools中からProgram FPGAを

選択する.

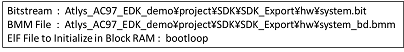

15. 書きこむファイルを選択する.

選択後Programをクリックし,FPGAに書き込まれる.

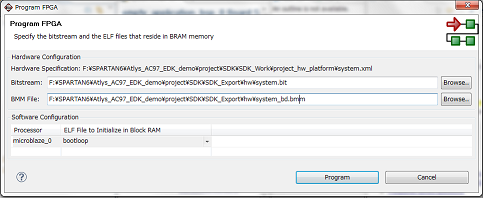

16. Project Exploler欄のempty_application_0を展開し,Binariesの項目からempty_application_0.elfを右クリック

する.Run As→Launch on Hardwareを選択すると,FPGAにソースコードが書きこまれ実行される.

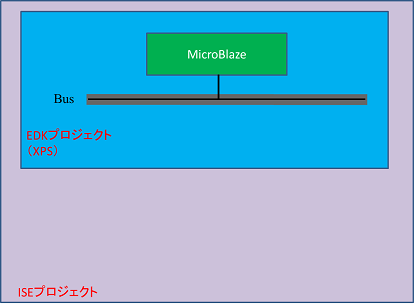

デモプロジェクトのままではISE上で作成したHW部(「3-1-1. Hardware Logic の設計」参照)とMicroBlazeをつなげることができないため, ISE上で接続できるように設定する.

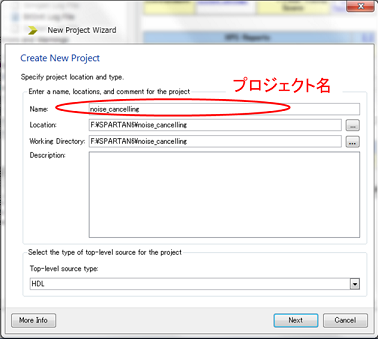

1. ISEを立ち上げ,画面上部のメニューの中からFile → New Project を選択するとNew Project Wizardが立ち

上がる.

2. Create New Projectのページではプロジェクト名と保存フォルダの場所を設定する.Top-level source typeが

HDLになっていることを確認したら,Nextをクリックする.

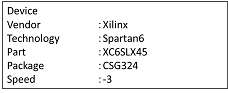

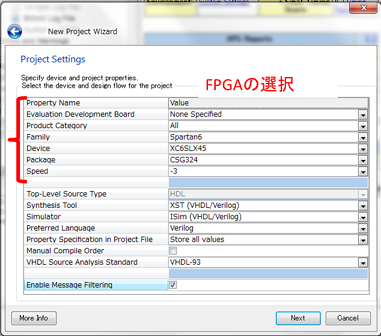

3. Project Settingsのページでは開発ターゲットデバイスの設定と開発ツールの設定を行う.図のように設定を行

い,終わったらNextをクリックする.

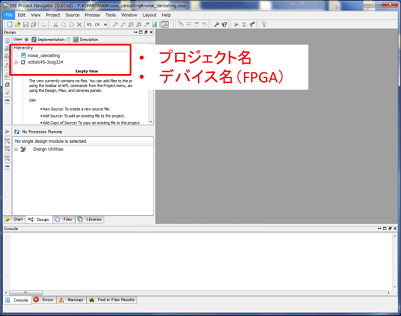

4. Project Summaryのページで設定に誤りがないか確認したらFinishをクリックし,New Project Wizardを閉じる.

ここまでで,ISEの空プロジェクトができた.

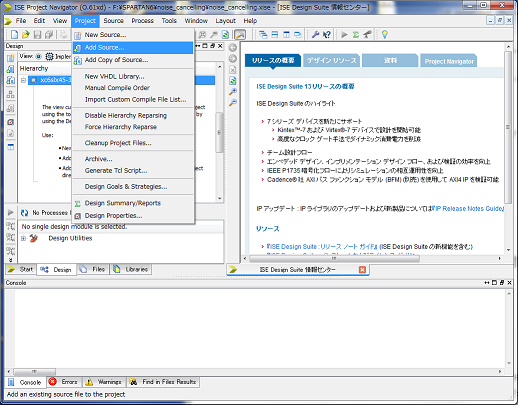

前項(ISE新規プロジェクトの作成)で空のISEプロジェクトができたので,ISEプロジェクト(noise_cancelling.xise)に EDKプロジェクト(system.xmp)を追加する.手順は以下のとおりである.

1. Atlys_AC97_EDK_demo\projectフォルダをISEプロジェクトのフォルダの下にコピーする.今回はこのフォルダ

名をDemoに変更した.

2. ISEプロジェクトを起動する.画面上部のメニューの中からProject → Add Sourceをクリックする.先ほどコピー

したDemoフォルダ内のsystem.xmpを選択する.

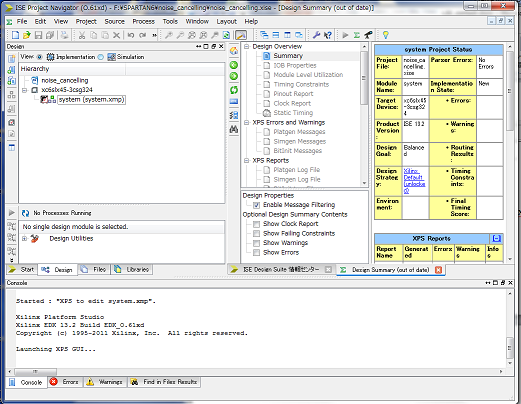

3. ISEプロジェクトにEDKが追加された.

これで,ISE上で設計したHW部とEDKプロジェクトの回路が接続可能になった.

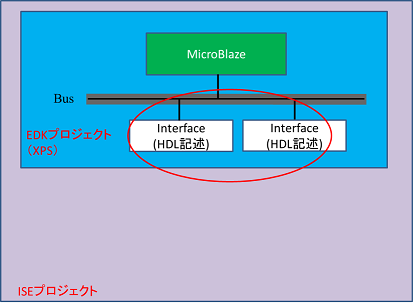

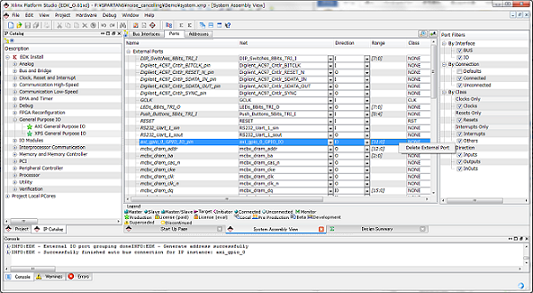

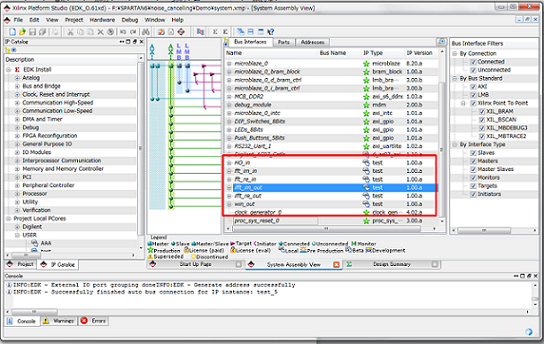

CPUとHW部を接続するためにEDKプロジェクト回路の外部へのインターフェースをXPSで追加する. 接続自体は次項(ISEでHW回路と統合)で ISE上にて行う.

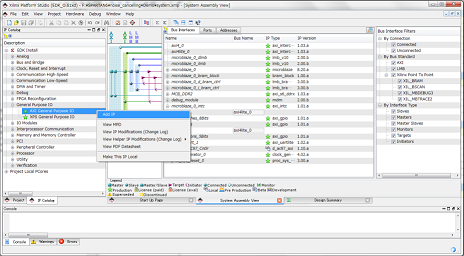

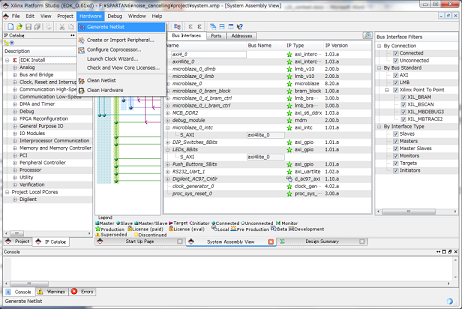

1. ISEのHierarchyの中のsystemをクリックし,Processesの中からManage Processor Design(xps) を選択すると

XPSが起動する.

2. “Create and Import Peripheral For Microblaze ver AXI.ppt(ここから)” を参考にペリフェラルの作成を行う.

3. ペリフェラルを追加するにはIP Catalog欄から追加したいIPを右クリック→Add IPをクリックする.

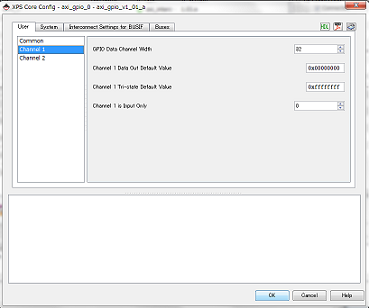

4. 追加するIPに応じた設定画面が表示されるので設定をおこなう.

5. ペリフェラルが追加される.尚,設定を変更したいときは右クリック→Configure IPで再設定可能.また,Delete

Instanceで削除される.

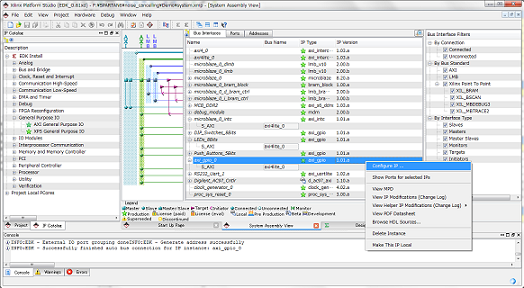

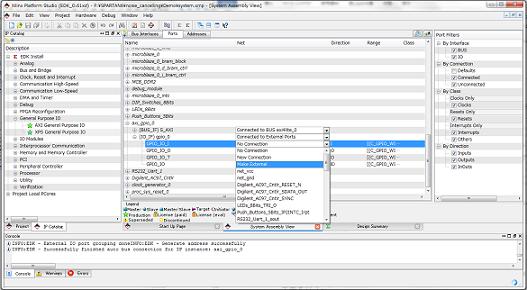

6. Portsタブ内ではペリフェラルの接続設定ができる.接続設定を行いたいペリフェラルを展開すると,ペリフェラ

ルのポートが表示される.XPS内でつなぎたいポートがある場合,New Connection又は選択肢から接続先を設

定する.XPSプロジェクト外で接続したい場合はMake Externalを選択する.

7. Make Externalを選択した場合External Ports の項目に追加される.

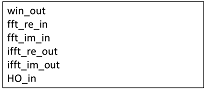

8. 今回は2で作成したtest IPを使用する.まず,test IPを6個追加する.その後,名前を以下のように変更する.

9. 上記6〜7を参考にポートの設定を行う.

win_out, ifft_re_out, ifft_im_outは以下のポートをExternal Portsに設定する.

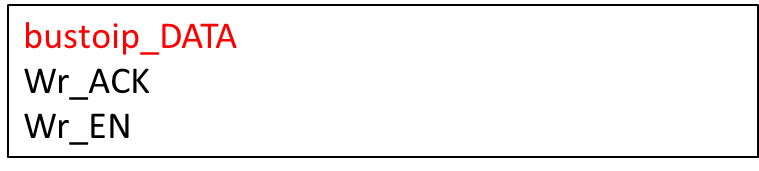

HO_in, fft_re_in, fft_im_inは以下のポートをExternal Portsに設定する.

※(2012/11/13) "iptobus_DATA"と"bustoip_DATA"の記述が逆になっていたので訂正しました.

10. XPSでの設計が終わったら,画面上部のメニューの中の Hardware → Generate Netlistを選択しネットリスト

の生成を行う.

11. xpsを閉じる.

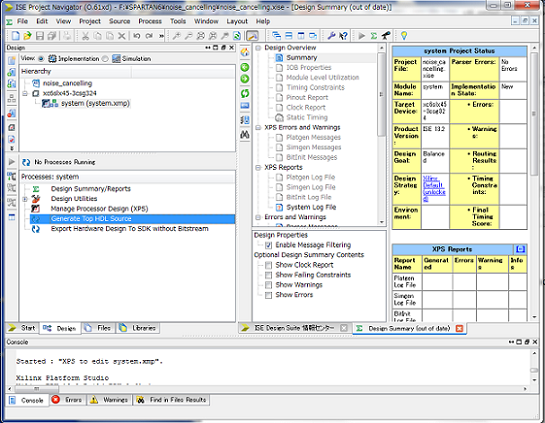

12. ISEのHierarchyの中のsystemをクリックし,Processesの中からGenerate Top HDL Sourceを選択する.

13. system_top.vが生成される.このファイルはDemoフォルダ内に生成される.これをISEプロジェクトのフォルダに

コピーする.

14. Hierarchyの中のsystem_top.vを右クリックしRemoveでプロジェクトから除外する.その後,Add SourceでISE

プロジェクトフォルダ直下のsystem_top.vファイルを追加する.このsystem_topモジュールが開発するシステム

のトップモジュールになる.

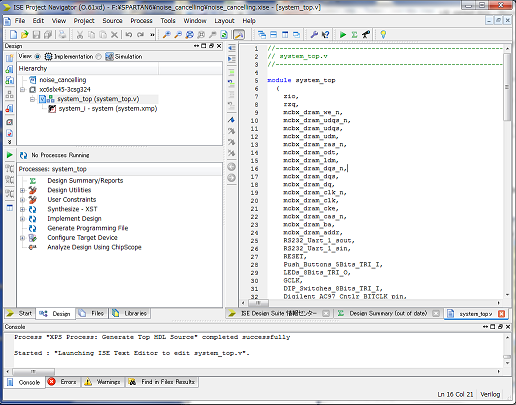

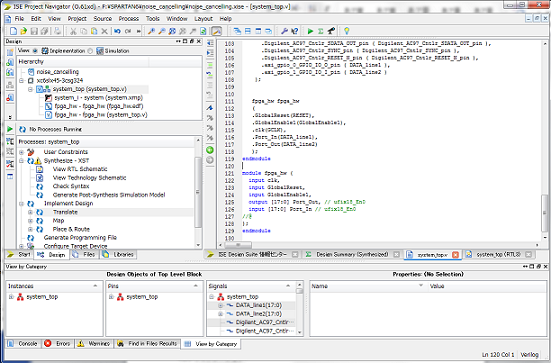

3-1-1.で作成したHW回路を,前項で作成したXPSでの回路とISE上で接続する.

1. ISEプロジェクトフォルダにsynphonyで作成したedfファイルをコピーし,Add Sourceでプロジェクトに追加する.

2. system_top.vにこの回路のモジュールをverilogで記述し,xpsプロジェクトで作成した回路のポートと接続させ

る.今回制作する回路のトップモジュール(system_top.v)はここからダウンロードできる.

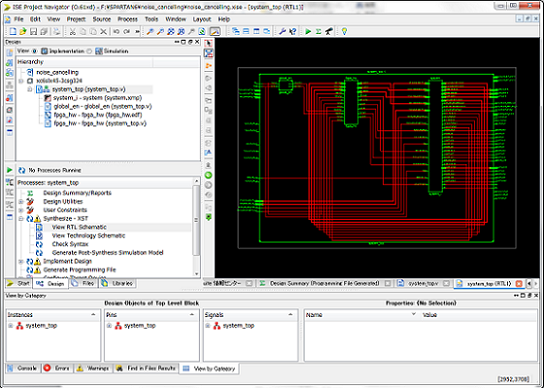

3. Processesの欄のSynthesize-XST→View RTL Schematicで回路構成をみることができる.

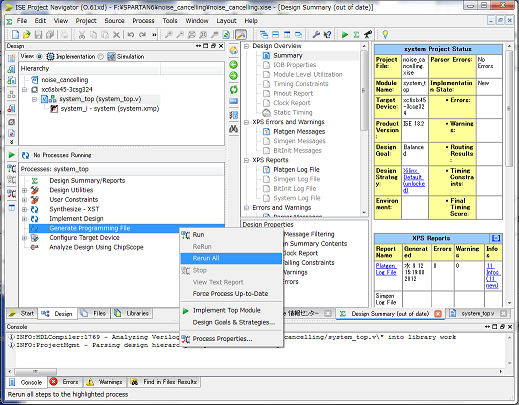

1. Hierarchy内のsystem_topを選択し,Processes欄の中のGenerate Programing Fileを右クリックし,Rerun All

を実行する.

2. Errorが出なければ,system_top.bitファイルがISEプロジェクトのフォルダ内に生成される.

ここまでで,HWの実装が完了した.