| Japanese | English |

第14回LSIデザインコンテスト・イン沖縄 設計仕様書 - 8

8. LEVEL1 初心者用課題

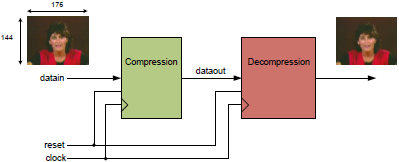

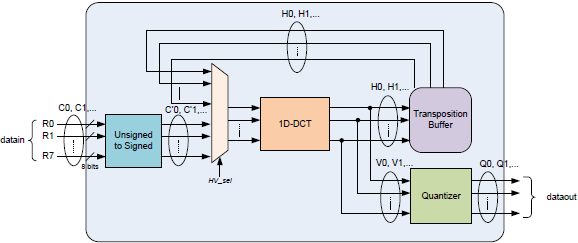

ここでは,図11に示すような圧縮・伸長システムを作成します。システムの入力はQCIFサイズの画像(176x144ピクセル)です。入力画像はY、Cr、Cbのブロックデータと呼ばれる、8x8のピクセルに分解されます。処理は、画像左上角部から始まり、右下角部で終わるラスタースキャン手法で行われます。圧縮機は図12で示されるブロックで構成されており、1D-DCTブロックは図5に示すアーキテクチャで構成されています。

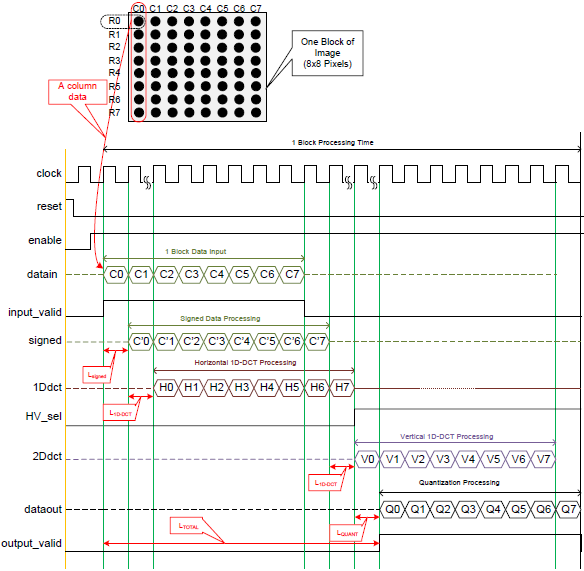

各データ処理ブロックのタイミングチャートを図13に示します。入力データは、圧縮機に列形式(C0,C1,,,C7)で入力されます。各列は、異なる行(R0,R1,,,R7)を持つ8ピクセルデータで構成されます。よって全てのデータブロックが入力されるのに8クロックのサイクルが必要となります。 シリアルで入力される入力信号は、vaild_inputで示されます。最初の列データC0の1クロックサイクル後に、signedはUnsigned to Signedブロックの出力となります。よってこのブロックの処理遅延(Lsigned)は1クロックサイクルとなります。

Unsigned to Signedブロックの出力は1D-DCTブロックに送られます。1D-DCTブロックの処理遅延(L1D-DCT)は、図5の1D-DCTブロックの構成方法に依存します。設計者は、このブロックの処理プロセスを複数のパイプラインステージに分割することもあります。1D-DCTブロックの出力はTransposition Bufferに保存されます。

1D-DCTブロックによって全ての1ピクセルブロックが処理された後、処理結果は1D-DCTブロックで、違う手順で再び処理されます。このときの処理遅延は先ほどと同様(L1D-DCT)になります。最初の列データが終わると同時に、処理結果はQuantizerブロックで演算されます。Quantizerブロックの処理遅延(LQUANT)は、Quantizerブロックの実装仕様とビット幅に依存します。結果的に、一つのピクセルデータブロックを処理するのに必要となる時間は、Lsigned、L1D-DCT、LQUANTに依存します。

Signed(Unsigned to Signed)、Transformation(1D-DCT)、Quantization(Quantizer)のプロセスは、enable信号がアクティブになったときに動作します。enable信号は、コアが新たな入力信号を受ける準備が整ったことを示す信号です。数処理遅延の後、vaild_output信号がアクティブになる際 に出力信号が認識されます。

画像品質を維持したまま、設計パラメータ(サイズ、スピード)を最適化するために、設計者は各処理ブロックのビット幅を最適化しなければなりません。これは固定小数点を用いて、処理シミュレーションを行うことによってできます。

図11 システム構成

図12 圧縮器ブロック図

図13 圧縮器タイミングダイアグラム

| No | Name Port | Description | Active | I/O | Width |

| 1 | clock | Clock signal | Input | 1 | |

| 2 | reset | Reset signal | Low | Input | 1 |

| 3 | enable | Indicates that the core is ready to receive new data | High | Input | 1 |

| 4 | cmode | Table quantization selector (Q50=0,Q80=1) | Input | 1 | |

| 5 | datain | Column input signal | Input | 64 | |

| 6 | valid_input | Sample the valid data at datain port | High | Input | 1 |

| 7 | valid_output | Validata the output data at dataout port | High | Output | 1 |

| 8 | dataout | Compressed image signal | Output | 64 |

表2 ポート定義